## Topics to be covered

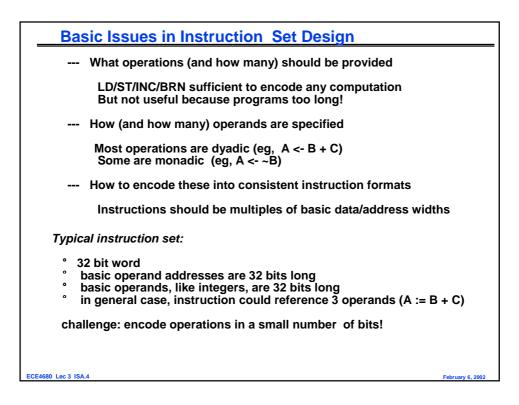

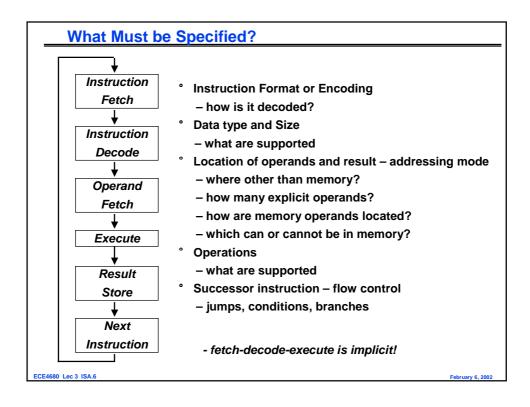

We will discuss the following topics which determines the Complexity of IS.

- Instruction Format or Encoding

how is it decoded?

- ° Data type and Size

- what are supported

- \* Location of operands and result addressing mode

- where other than memory?

- how many explicit operands?

- how are memory operands located?

- which can or cannot be in memory?

- ° Operations

- what are supported

- ° Successor instruction flow control

- jumps, conditions, branches

ECE4680 Lec 3 ISA.7

| Basic ISA Classes                                                      |                                         |                                   |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|--|--|--|

| Accumulator: (earliest machines)                                       |                                         |                                   |  |  |  |

| 1 address                                                              | add A                                   | $acc \leftarrow acc + mem[A]$     |  |  |  |

| 1+x address                                                            | addx A                                  | $acc \leftarrow acc + mem[A + x]$ |  |  |  |

| <u>Stack: (</u> HP calc                                                | culator, Java virt                      | ual machines <u>)</u>             |  |  |  |

| 0 address                                                              | add                                     | tos ← tos + next                  |  |  |  |

| <u>General Purpose Register: (</u> e.g. Intel 80x86, Motorola 68xxx)   |                                         |                                   |  |  |  |

| 2 address                                                              | add A B                                 | $EA(A) \leftarrow EA(A) + EA(B)$  |  |  |  |

| 3 address                                                              | add A B C                               | $EA(A) \leftarrow EA(B) + EA(C)$  |  |  |  |

| Load/Store: (e.g                                                       | Load/Store: (e.g. SPARC, MIPS, PowerPC) |                                   |  |  |  |

| 3 address                                                              | add Ra Rb Rc                            | Ra ← Rb + Rc                      |  |  |  |

|                                                                        | load Ra Rb                              | Ra ← mem[Rb]                      |  |  |  |

|                                                                        | store Ra Rb                             | mem[Rb] ← Ra                      |  |  |  |

| Comparison:                                                            |                                         |                                   |  |  |  |

| Bytes per instruction? Number of Instructions? Cycles per instruction? |                                         |                                   |  |  |  |

| ECE4680 Lec 3 ISA.8                                                    |                                         | February 6, 2002                  |  |  |  |

| Compa                            | ring Instruction    | IS                         |                  |  |  |

|----------------------------------|---------------------|----------------------------|------------------|--|--|

| Comparing Number of Instructions |                     |                            |                  |  |  |

| ° Code sequ                      | ience for C = A + B | for four classes of instru | uction sets:     |  |  |

| Stack                            | Accumulator         | Register                   | Register         |  |  |

|                                  |                     | (register-memory)          | (load-store)     |  |  |

| Push A                           | Load A              | Load R1,A                  | Load R1,A        |  |  |

| Push B                           | Add B               | Add R1,B                   | Load R2,B        |  |  |

| Add                              | Store C             | Store C, R1                | Add R3,R1,R2     |  |  |

| Рор С                            |                     |                            | Store C,R3       |  |  |

|                                  |                     |                            |                  |  |  |

|                                  |                     |                            |                  |  |  |

|                                  |                     |                            |                  |  |  |

|                                  |                     |                            |                  |  |  |

|                                  |                     |                            |                  |  |  |

| ECE4680 Lec 3 ISA.9              |                     |                            | February 6, 2002 |  |  |

| <u> </u>      | xample   | es of Register Usage                               |                  |

|---------------|----------|----------------------------------------------------|------------------|

| Num           | ber of m | emory addresses per typical ALU instruction        |                  |

|               |          | mum number of operands per typical ALU instruction |                  |

|               |          | Examples                                           |                  |

| 0             | 3        | SPARC, MIPS, Precision Architecture, Power PC      |                  |

| 1             | 2        | Intel 80x86, Motorola 68000                        |                  |

| 2             | 2        | VAX (also has 3-operand formats)                   |                  |

| 3             | 3        | VAX (also has 2-operand formats)                   |                  |

|               |          |                                                    |                  |

|               |          |                                                    |                  |

|               |          |                                                    |                  |

| ECE4680 Lec 3 | ISA.12   |                                                    | February 6, 2002 |

| Example:             |                                                                  |                                            |

|----------------------|------------------------------------------------------------------|--------------------------------------------|

| In VAX:              | ADDL (R9), (R10), (I<br>mem[R9] <-                               | <mark>R11)</mark><br>- mem[R10] + mem[R11] |

| In MIPS:             | lw R1, (R10);<br>lw R2, (R11)<br>add R3, R1, R2;<br>sw R3, (R9); | load a word<br>R3 < R1+R2<br>store a word  |

| ECE4680 Lec 3 ISA.13 |                                                                  | February 6, 2002                           |

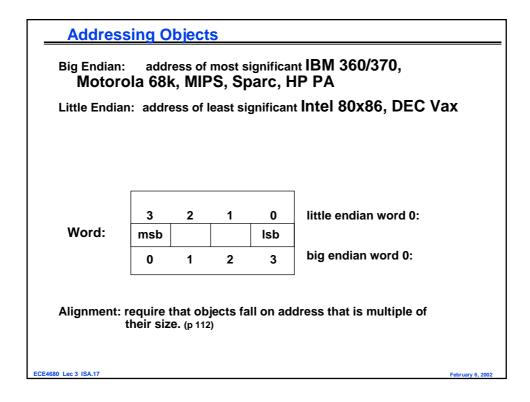

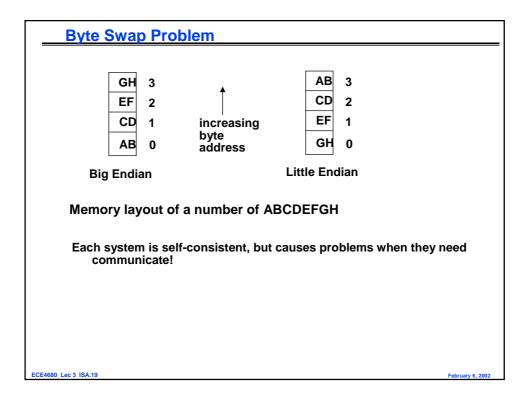

| BIG Endian versus Little En | ndian (P113 & A-46)      |

|-----------------------------|--------------------------|

| Example 1: Memory layout o  | of a number #ABCD        |

| In Big Endian:<br>──→       | CD \$1001<br>▶ AB \$1000 |

| In Little Endian:<br>──→    | AB \$1001<br>► CD \$1000 |

| Example 2: Memory layout of | a number #FF00           |

|                             |                          |

|                             |                          |

| ECE4680 Lec 3 ISA.18        | February 6, 2002         |

| Addressing mode    | Example            | Meaning                                                     |

|--------------------|--------------------|-------------------------------------------------------------|

| Immediate          | Add R4,#3          | R4 ← R4+3                                                   |

| Register           | Add R4,R3          | R4 ← R4+R3                                                  |

| Register indirect  | Add R4,(R1)        | R4 ← R4+Mem[R1]                                             |

| Displacement       | Add R4,100(R1)     | R4 ← R4+Mem[100+R1]                                         |

| Indexed            | Add R3,(R1+R2)     | $R3 \leftarrow R3+Mem[R1+R2]$                               |

| Direct or absolute | Add R1,(1001)      | R1 ← R1+Mem[1001]                                           |

| Memory indirect    | Add R1,@(R3)       | $R1 \leftarrow R1 + Mem[Mem[R3]]$                           |

| Auto-increment     | Add R1,(R2)+       | $R1 \leftarrow R1\text{+}Mem[R2]; R2 \leftarrow R2\text{+}$ |

| Auto-decrement     | Add R1,-(R2)       | $R2 \leftarrow R2-d; R1 \leftarrow R1+Mem[R2]$              |

| Scaled             | Add R1,100(R2)[R3] | R1 ← R1+Mem[100+R2+R3*d]                                    |

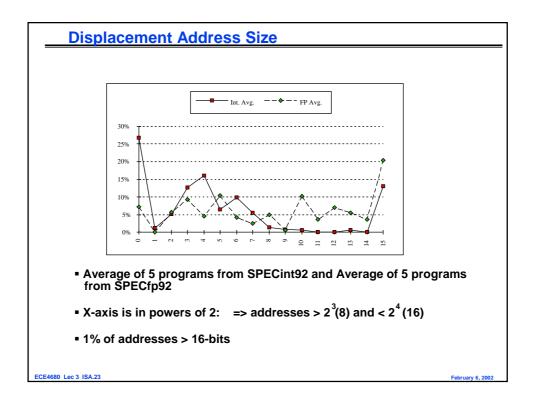

| Addressing Mode Usage         |                    |                  |

|-------------------------------|--------------------|------------------|

| 3 programs avg, 17% to 43%    |                    |                  |

| Register deferred (indirect): | 13% avg, 3% to 24% |                  |

| Scaled:                       | 7% avg, 0% to 16%  |                  |

| Memory indirect:              | 3% avg, 1% to 6%   |                  |

| Misc:                         | 2% avg, 0% to 3%   |                  |

|                               |                    |                  |

|                               |                    |                  |

|                               |                    |                  |

| ECE4680 Lec 3 ISA.22          |                    | February 6, 2002 |

| Typical Operations    |                                                                                                                                                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Movement         | Load (from memory)<br>Store (to memory)<br>memory-to-memory move<br>register-to-register move<br>input (from I/O device)<br>output (to I/O device)<br>push, pop (to/from stack) |

| Arithmetic            | integer (binary + decimal) or FP<br>Add, Subtract, Multiply, Divide                                                                                                             |

| Logical               | not, and, or, set, clear                                                                                                                                                        |

| Shift                 | shift left/right, rotate left/right                                                                                                                                             |

| Control (Jump/Branch) | unconditional, conditional                                                                                                                                                      |

| Subroutine Linkage    | call, return                                                                                                                                                                    |

| Interrupt             | trap, return                                                                                                                                                                    |

| Synchronization       | test & set (atomic r-m-w)                                                                                                                                                       |

| String                | search, translate                                                                                                                                                               |

| Lec 3 ISA.26          | February                                                                                                                                                                        |

## Top 10 80x86 Instructions

| 1       | load                    | r Average Percent total executed<br>22% |  |

|---------|-------------------------|-----------------------------------------|--|

| •       |                         |                                         |  |

| 2       | conditional branch      | 20%                                     |  |

| 3       | compare                 | 16%                                     |  |

| 4       | store                   | 12%                                     |  |

| 5       | add                     | 8%                                      |  |

| 6       | and                     | 6%                                      |  |

| 7       | sub                     | 5%                                      |  |

| В       | move register-register  | 4%                                      |  |

| 9       | call                    | 1%                                      |  |

| 10      | return                  | 1%                                      |  |

|         | Total                   | 96%                                     |  |

| ° Simpl | e instructions dominate | instruction frequency                   |  |

| •       |                         |                                         |  |

|         |                         |                                         |  |

| ° Con | dition Codes        |                                                                          |  |

|-------|---------------------|--------------------------------------------------------------------------|--|

| inst  |                     | set as a side-effect of arithmetic<br>Moves) or explicitly by compare or |  |

| ex:   | add r1, r2, r3      |                                                                          |  |

|       | bz label            |                                                                          |  |

| ° Con | dition Register     |                                                                          |  |

| Ex:   | cmp r1, r2, r3; com | npare r2 with r3, 0 or 1 is stored in r1                                 |  |

|       | bgt r1, label; bra  | inch on greater                                                          |  |

| ° Con | pare and Branch     |                                                                          |  |

| Ex:   | bgt r1, r2, label;  | if r1 > r2, then go to label                                             |  |

|       |                     |                                                                          |  |

|       |                     |                                                                          |  |

|       |                     |                                                                          |  |

| Condition Cod                                                                                                                                                                                                                                                                                                                                                               | <u>les</u> |        |                                 |                  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|---------------------------------|------------------|--|

| Setting CC as side effect can reduce the # of instructions                                                                                                                                                                                                                                                                                                                  |            |        |                                 |                  |  |

| X: .                                                                                                                                                                                                                                                                                                                                                                        | X: .       |        |                                 |                  |  |

| •                                                                                                                                                                                                                                                                                                                                                                           |            | versus | •                               |                  |  |

| SUB r0,#1,<br>BRP X                                                                                                                                                                                                                                                                                                                                                         | rO         |        | SUB r0, #<br>CMP r0, #<br>BRP X |                  |  |

| But also has dis                                                                                                                                                                                                                                                                                                                                                            | advantage  | S:     |                                 |                  |  |

| <ul> <li>not all instructions set the condition codes<br/>which do and which do not often confusing!<br/><i>e.g., shift instruction sets the carry bit</i></li> <li>dependency between the instruction that sets the CC and the one<br/>that tests it: to overlap their execution, may need to separate them<br/>with an instruction that does not change the CC</li> </ul> |            |        |                                 |                  |  |

| ifetch read compute write                                                                                                                                                                                                                                                                                                                                                   |            |        |                                 |                  |  |

| Old CC read New CC computed                                                                                                                                                                                                                                                                                                                                                 |            |        |                                 |                  |  |

|                                                                                                                                                                                                                                                                                                                                                                             | ifetch     | read   | compute                         | write            |  |

| ECE4680 Lec 3 ISA.29                                                                                                                                                                                                                                                                                                                                                        |            |        |                                 | February 6, 2002 |  |

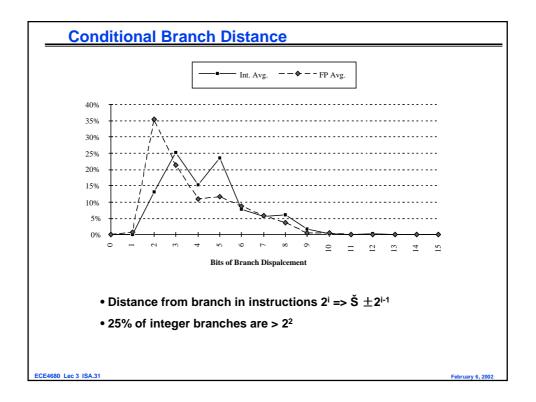

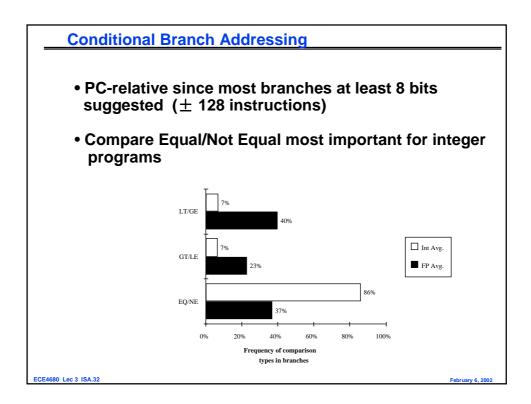

| Branches                                                                                                                                                                                                                          |                                                                                                                                                            |                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Conditional control transfers                                                                                                                                                                                                     | 8                                                                                                                                                          |                  |

| <i>Four basic conditions:</i><br>N negative<br>Z zero                                                                                                                                                                             | V overflow<br>C carry                                                                                                                                      |                  |

| Sixteen combinations of the bas                                                                                                                                                                                                   | ic four conditions:                                                                                                                                        |                  |

| Always<br>Never<br>Not Equal<br>Equal<br>Greater<br>Less or Equal<br>Greater or Equal<br>Less<br>Greater Unsigned<br>Less or Equal Unsigned<br>Carry Clear<br>Carry Set<br>Positive<br>Negative<br>Overflow Clear<br>Overflow Set | Unconditional<br>NOP<br>~Z<br>Z<br>~[Z + (N $\otimes$ V)]<br>Z + (N $\otimes$ V)<br>~(N $\otimes$ V)<br>~(C + Z)<br>C + Z<br>~C<br>C<br>~N<br>N<br>~V<br>V |                  |

| ECE4680 Lec 3 ISA.30                                                                                                                                                                                                              |                                                                                                                                                            | February 6, 2002 |

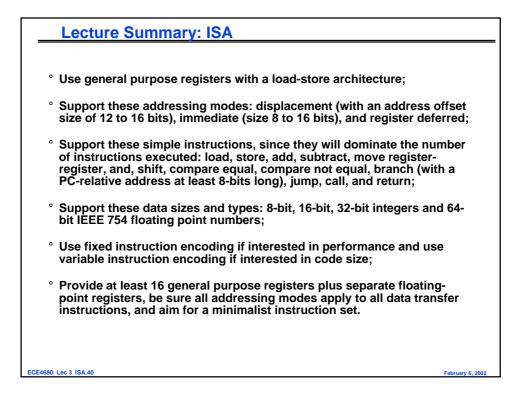

## **Operation Summary**

• Support these simple instructions, since they will dominate the number of instructions executed:

| load,                                                     |  |

|-----------------------------------------------------------|--|

| store,                                                    |  |

| add,                                                      |  |

| subtract,                                                 |  |

| move register-register,                                   |  |

| and,                                                      |  |

| shift,                                                    |  |

| compare equal, compare not equal,                         |  |

| branch (with a PC-relative address at least 8-bits long), |  |

| jump,                                                     |  |

| call,                                                     |  |

| return;                                                   |  |

| ,                                                         |  |

|                                                           |  |

ECE4680 Lec 3 ISA.33

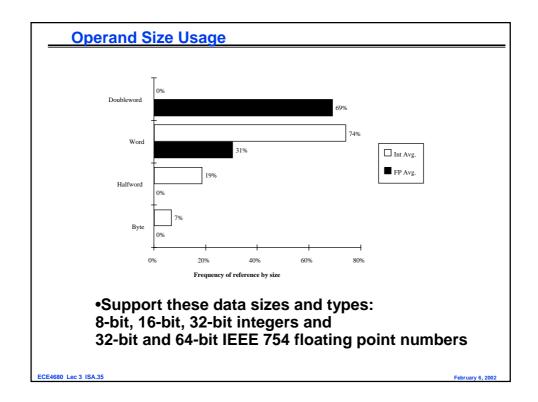

| Data Types                                                                                                                                   |                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <u>Bit</u> : 0, 1                                                                                                                            |                                                                                    |

| Bit String: sequence of bits of a particular length<br>4 bits is a nibble<br>8 bits is a byte<br>16 bits is a half-word<br>32 bits is a word |                                                                                    |

| <u>Character:</u><br>ASCII 7 bit code<br>EBCDIC 8 bit code (IBM)<br>UNICODE 16 bit code (Java)                                               |                                                                                    |

| <u>Decimal:</u><br>digits 0-9 encoded as 0000b thru 1001b<br>two decimal digits packed per 8 bit byte                                        |                                                                                    |

| Integers:<br>Sign & Magnitude: 0X vs. 1X<br>1's Complement: 0X vs. 1(~X)<br>2's Complement: 0X vs. (1's comp) + 1                            | Positive #'s same in all<br>First 2 have two zeros<br>Last one usually chosen      |

| ECE4660 Lec 3 ISA.34                                                                                                                         | How many +/- #'s?<br>Where is decimal pt?<br>How are +/- exponents<br>represented? |

| Generic Exa          | mples of | Instruc | tion Forma | ats |                  |

|----------------------|----------|---------|------------|-----|------------------|

|                      |          |         |            |     |                  |

|                      |          |         |            |     |                  |

| Variable:            |          |         |            |     |                  |

|                      |          |         |            |     |                  |

| Fixed:               |          |         |            |     |                  |

| Hybrid:              |          |         |            |     |                  |

|                      |          |         |            |     |                  |

|                      |          |         |            |     | _                |

|                      |          |         |            |     |                  |

|                      |          |         |            |     |                  |

|                      |          |         |            |     |                  |

|                      |          |         |            |     |                  |

| ECE4680 Lec 3 ISA.37 |          |         |            |     | February 6, 2002 |