# ECE4680 Computer Organization & Architecture MIPS Instruction Set Architecture Why is MIPS a good example? Learn ISA further by this example. How does IS fill up the gap between HLL and machine?

ECE4680 Lec4 MIPS.1

### **RISC Vs. CISC**

### RISC→CISC

80 Lec4 MIPS.2

ary 6, 2003

- ° Determined by VLSI technology.

- Software cost goes up constantly. To be convenient for programmers.

To shorten the semantic gap between HLL and architecture without advanced compilers.

- $^{\circ}\,$  To reduce the program length because memory was expensive.

- ° VAX 11/780 reached the climax with >300 instructions and >20 addressing modes. CISC → RISC

- ° Things changed: HLL, Advanced Compiler, Memory size, ...

- ° Finding: 25% instructions used in 95% time.

- ° Size: usually <100 instructions and <5 addressing modes.

- ° Other properties: fixed instruction format, register based, hardware control...

- ° Gains: CPI is smaller, Clock cycle shorter, Hardware simpler, Pipeline easier

February 6, 2002

- <sup>o</sup> Loss: Program becomes longer, but memory becomes larger and larger, cheaper and cheaper. Programmability becomes poor, but people use HLL instead of IS.

- $^{\circ}\,$  Result: although program is prolonged, the total gain is still a plus.

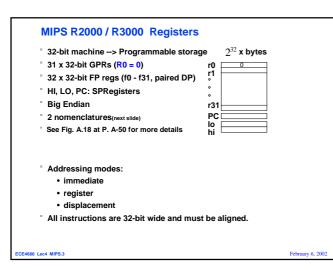

| 2 1     | lomenc  | menclatures of MIPS Registers (p.140, A-23)                      |                   |  |  |  |

|---------|---------|------------------------------------------------------------------|-------------------|--|--|--|

| Name    | number  | Usage                                                            | Reserved on call? |  |  |  |

| zero    | 0       | constant value =0                                                | n.a.              |  |  |  |

| at      | 1       | reserved for assembler (p.147,157)                               | n.a.              |  |  |  |

| v0 – v1 | 2 – 3   | values for results and expression evaluation                     | no                |  |  |  |

| a0 – a3 | 4 – 7   | arguments no                                                     |                   |  |  |  |

| t0 - t7 | 8 – 15  | temporaries no                                                   |                   |  |  |  |

| s0 – s7 | 16 – 23 | saved yes                                                        |                   |  |  |  |

| t8 – t9 | 24 – 25 | more temporaries no                                              |                   |  |  |  |

| k0 – k1 | 26 – 27 | Reserved for kernel n.a.                                         |                   |  |  |  |

| gp      | 28      | global pointer yes                                               |                   |  |  |  |

| sp      | 29      | stack pointer yes                                                |                   |  |  |  |

| fp      | 30      | frame pointer yes                                                |                   |  |  |  |

| ra      | 31      | return address                                                   | yes               |  |  |  |

| zero at | t vo-v1 | a0 - a3 t0 - t7 s0 - s7 t8 - t9 k0 - k                           | al gp sp fp ra    |  |  |  |

| 0 1     | 2 - 3   | 4 - 7 8 15 16 23 24 - 25 26 - 27 28 29 30 31<br>February 6, 2002 |                   |  |  |  |

| MIPS arit           | hmetic and       | logic instruc          | rtions                         |

|---------------------|------------------|------------------------|--------------------------------|

|                     | innetio unu      | logio moti ut          |                                |

| Instruction         | Example          | Meaning                | Comments                       |

| add                 | add \$1,\$2,\$3  | 1 = 2 + 3              | 3 operands; exception possible |

| subtract            | sub \$1,\$2,\$3  | 1 = 2 - 3              | 3 operands; exception possible |

| add immediate       | addi \$1,\$2,100 | 1 = 2 + 100            | + constant; exception possible |

| multiply            | mult \$2,\$3     | Ui I a = \$2 x \$3     | 64-bit signed product          |

| • •                 |                  |                        | · ·                            |

| divide              | div \$2,\$3      | $Lo = $2 \div $3,$     | Lo = quotient, Hi = remainder  |

|                     |                  |                        | Hi = \$2 mod \$3               |

| Move from Hi        | mfhi \$1         | \$1=Hi                 | get a copy of Hi               |

| Move from Lo        | mflo \$1         | \$1=lo                 |                                |

|                     |                  |                        |                                |

| Instruction         | Example          | Meaning                | Comment                        |

| and                 | and \$1,\$2,\$3  | \$1 = \$2 & \$3        | Logical AND                    |

| or                  | or \$1,\$2,\$3   | \$1 = \$2   \$3        | Logical OR                     |

| xor                 | xor \$1,\$2,\$3  | <b>\$1 = \$2 ⊕ \$3</b> | Logical XOR                    |

| nor                 | nor \$1,\$2,\$3  | \$1 = ~(\$2  \$3)      | Logical NOR                    |

|                     |                  |                        |                                |

| ECE4680 Lec4 MIPS.5 |                  |                        | February 6, 2002               |

## Example (p110)

E.g. f = (g+h) - (i+j), assuming f, g, h, i, j be assigned to \$1, \$2, \$3, \$4, \$5

> add \$7, \$2, \$3 add \$8, \$4, \$5 sub \$1, \$7, \$8

ECE4680 Lec4 MIPS.6

February 6, 2002

| MIPS data transfer inst | tructions        |                  |

|-------------------------|------------------|------------------|

| Instruction             | Comment          |                  |

| SW 500(\$4), \$3        | Store word       |                  |

| SH 502(\$2), \$3        | Store half       |                  |

| SB 41(\$3), \$2         | Store byte       |                  |

| LW \$1, 30(\$2)         | Load word        |                  |

| LH \$1, 40(\$3)         | Load half a word |                  |

| LB \$1, 40(\$3)         | Load byte        |                  |

|                         |                  |                  |

|                         |                  |                  |

|                         |                  |                  |

|                         |                  |                  |

|                         |                  |                  |

| ECE4680 Lec4 MIPS.7     |                  | February 6, 2002 |

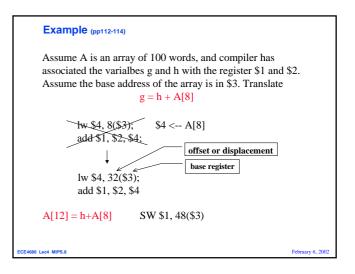

| Assume A is an array of 100 associated the varialbes g, h, | words, and compiler has<br>and i with the register \$1, \$2, \$5. |

|------------------------------------------------------------|-------------------------------------------------------------------|

| Assume the base address of t                               | the array is in \$3. Translate                                    |

| g = h -                                                    | + A[i]                                                            |

| add; ¢6 ¢0 4.                                              | \$6 = 4                                                           |

| addi \$6, \$0, 4;<br>mult \$5, \$6;                        | 30 = 4<br>Hi,Lo = i*4                                             |

| mflo \$6;                                                  | $6 = i^4$ , assuming i is small                                   |

| add \$4, \$3, \$6;                                         | $4 \leftarrow address of A[i]$                                    |

| add \$1, \$2, \$4                                          |                                                                   |

|                                                            |                                                                   |

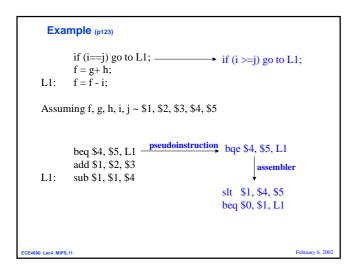

| Instruction        | Example                               | Meaning                                                      |  |

|--------------------|---------------------------------------|--------------------------------------------------------------|--|

| branch on equal    | beq \$1,\$2,100<br>Equal test; PC rel | if (\$1 == \$2) go to PC+4+100<br>lative branch              |  |

| branch on not eq.  | bne \$1,\$2,100<br>Not equal test; PC | if (\$1!= \$2) go to PC+4+100<br>C relative                  |  |

| Pseudoinstruction  | blt, ble, bgt, bge                    | not implemented by hardware,<br>but synthesized by assembler |  |

| set on less than   | slt \$1,\$2,\$3<br>Compare less tha   | if (\$2 < \$3) \$1=1; else \$1=0<br>n; 2's comp.             |  |

| set less than imm. | slti \$1,\$2,100<br>Compare < const   | if (\$2 < 100) \$1=1; else \$1=0<br>ant; 2's comp.           |  |

| jump               | j 10000<br>Jump to target ad          | go to 10000<br>Idress                                        |  |

| jump register      | jr \$31<br>For switch, procee         | go to \$31<br>dure return                                    |  |

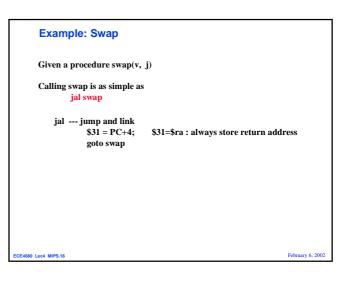

| jump and link      | jal 10000<br>For procedure cal        | \$31 = PC + 4; go to 10000                                   |  |

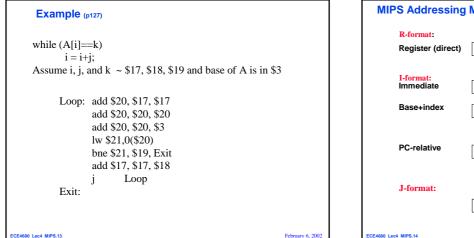

| Example (p    | 126)                                    |                    |

|---------------|-----------------------------------------|--------------------|

| Loop: g =     | g +A[i];                                |                    |

| i =           | i+ j;                                   |                    |

| if (i         | != h) go to Loop:                       |                    |

| of array is i | in \$5                                  |                    |

| of allay is   | in 45                                   |                    |

| Loop:         | add \$7, \$3, \$3;                      | i*2                |

|               | add \$7, \$7, \$7;                      | i*4                |

|               | add \$7, \$7, \$5                       |                    |

|               |                                         |                    |

|               | lw \$6, 0(\$7);                         | \$6=A[i]           |

|               | lw \$6, 0(\$7);<br>add \$1, \$1, \$6;   | f=A[i]<br>g=g+A[i] |

|               |                                         |                    |

|               | add \$1, \$1, \$6;<br>add \$3, \$3, \$4 |                    |

|               | add \$1, \$1, \$6;                      |                    |

|               | add \$1, \$1, \$6;<br>add \$3, \$3, \$4 |                    |

| Assume swap is ca<br>Assume temp is re<br>Write MIPS code |            | •                  | and k ~ \$16 and \$17;       |

|-----------------------------------------------------------|------------|--------------------|------------------------------|

| swap(int v[], int k)                                      |            |                    |                              |

| {<br>int temp;<br>temp = v[k];                            |            |                    |                              |

| v[k] = v[k+1];                                            | sll        | \$18, \$17, 2      | ; mulitply k by 4            |

| v[k+1] = temp;                                            | addu       | \$18, \$18, \$16   | ; address of v[k]            |

| }                                                         | lw         | \$15, 0(\$18)      | ; load v[k]                  |

|                                                           | lw         | \$19, 4(\$18)      | ; load v[k+1]                |

|                                                           | sw         | \$19, 0(\$18)      | ; store v[k+1] into v[k]     |

| Registers \$15, \$16,                                     | sw         | \$15, 4(\$18)      | ; store old v[k] into v[k+1] |

|                                                           | \$17, \$18 | , \$19 are occupie | d by caller ??               |

| swap:       |                                 |                                      |                  |                                                                                                   |                 |

|-------------|---------------------------------|--------------------------------------|------------------|---------------------------------------------------------------------------------------------------|-----------------|

| addi        | \$sp,\$sp, –24                  | ; Make room on stack for 6 registers |                  | ° Intel 8086/88 => 80286 => 80386 => 80486 => Pentium => P6                                       |                 |

| sw          | \$31, 20(\$sp)                  | ; Save return address                |                  | <ul> <li>8086 few transistors to implement 16-bit microprocessor</li> </ul>                       |                 |

| sw          | \$15, 16(\$sp)                  | ; Save registers on stack            |                  | <ul> <li>tried to be somewhat compatible with 8-bit microprocessor 80</li> </ul>                  | 80              |

| sw<br>sw    | \$16, 12(\$sp)<br>\$17, 8(\$sp) |                                      |                  | <ul> <li>successors added features which were missing from 8086 over<br/>next 15 years</li> </ul> | er              |

| sw          | \$18, 4(\$sp)                   |                                      |                  | <ul> <li>product of several different Intel engineers over 10 to 15 years</li> </ul>              | 5               |

| sw          | \$19, 0(sp)                     |                                      |                  | Announced 1978                                                                                    |                 |

|             |                                 |                                      |                  | ° VAX simple compilers & small code size =>                                                       |                 |

| lw          | \$19, 0(\$sp)                   | ; Restored registers from stack      |                  | efficient instruction encoding                                                                    |                 |

| lw          | \$18, 4(\$sp)                   |                                      |                  | powerful addressing modes                                                                         |                 |

| lw          | \$17, 8(\$sp)                   |                                      |                  | <ul> <li>powerful instructions</li> </ul>                                                         |                 |

| lw          | \$16, 12(\$sp)                  |                                      |                  | few registers                                                                                     |                 |

| lw          | \$15, 16(\$sp)                  |                                      |                  | <ul> <li>product of a single talented architect</li> </ul>                                        |                 |

| lw          | \$31, 20(\$sp)                  | ; Restore return address             |                  | Announced 1977                                                                                    |                 |

| addi        | \$sp,\$sp, 24                   | ; restore top of stack               |                  |                                                                                                   |                 |

| jr          | \$31                            | ; return to place that called swap   |                  |                                                                                                   |                 |

| 680 Lec4 MI | PS 10                           |                                      | February 6, 2002 | ECE4680 Lec4 MIPS.20                                                                              | February 6, 200 |

| Machine Evennlage    |                                                                                                   |                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Machine Examples:    | Address & Regi                                                                                    | sters                                                                             |

| Intel 8086           | 2 <sup>20</sup> x 8 bit bytes<br>AX, BX, CX, DX<br>SP, BP, SI, DI<br>CS, SS, DS<br>IP, Flags      | acc, index, count, quot<br>stack, string<br>code,stack,data segment               |

| VAX 11               | 2 <sup>32</sup> x 8 bit bytes<br>16 x 32 bit GPRs                                                 | r15 program counter<br>r14 stack pointer<br>r13 frame pointer<br>r12 argument ptr |

| MC 68000             | 24<br>2 x 8 bit bytes<br>8 x 32 bit GPRs<br>7 x 32 bit addr reg<br>1 x 32 bit SP<br>1 x 32 bit PC |                                                                                   |

| MIPS                 | 2 x 8 bit bytes<br>32 x 32 bit GPRs<br>32 x 32 bit GPRs<br>32 x 32 bit FPRs<br>HI, LO, PC         |                                                                                   |

| ECE4680 Lec4 MIPS.21 |                                                                                                   | February 6, 2002                                                                  |

# Homework 2, due Feb. 20, 2002 <sup>o</sup> Questions 3.2, 3.3, 3.5, 3.6, 3.7, 3.9, 3.11 <sup>o</sup> To answer question 3.7, please refer to Figure 3.13 (page 140) for register convention

° To answer 3.11, please refer to sort example in pages 166 for a skeleton of for loop

ECE4680 Lec4 MIPS.22

February 6, 2002