# Computer Organization and Architecture

Chapter 9 Computer Arithmetic

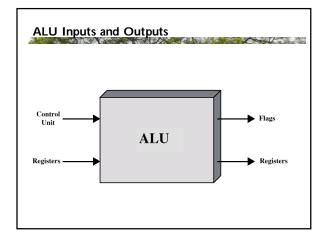

### Arithmetic & Logic Unit

Performs arithmetic and logic operations on data - everything that we think of as "computing."

- Everything else in the computer is there to service this unit

- All ALUs handle integers

- Some may handle floating point (real) numbers

- May be separate FPU (math co-processor)

- FPU may be on separate chip (486DX +)

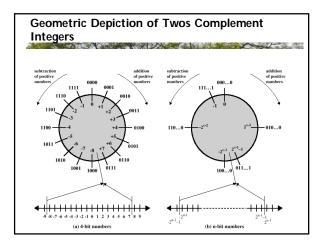

| Integer Representation                                                                                     |

|------------------------------------------------------------------------------------------------------------|

| <ul> <li>We have the smallest possible alphabet: the<br/>symbols 0 &amp; 1 represent everything</li> </ul> |

| No minus sign                                                                                              |

| No period                                                                                                  |

| Signed-Magnitude                                                                                           |

| Two's complement                                                                                           |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

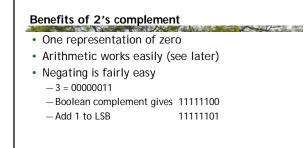

### 2's complement negation

• "Taking the 2's complement" (complement and add 1) is computing the arithmetic negation of a number

- Compute y = 0 x

Or

- Compute y such that x + y = 0

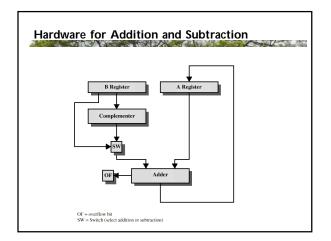

### Carry look-ahead

- · Carry look-ahead is expensive

- If n is the number of bits in a ripple adder, the circuit complexity (number of gates) is O(n)

- For full carry look-ahead, the complexity is  $O(n^{3}) \label{eq:carry}$

- Complexity can be reduced by rippling smaller look-aheads: e.g., each 16 bit group is handled by four 4-bit adders and the 16-bit adders are rippled into a 64-bit adder

### Multiplication

- A complex operation compared with addition and subtraction

- Many algorithms are used, esp. for large numbers

- Simple algorithm is the same long multiplication taught in grade school

- Compute partial product for each digit

- Add partial products

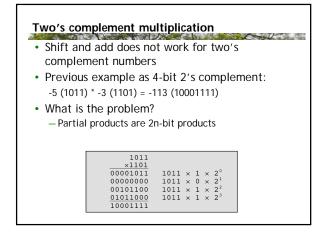

## Multiplication Example

• 1011 Multiplicand (11 dec)

A PARTY AND

- x 1101 Multiplier (13 dec)

- 1011 Partial products

- <u>0000</u> Note: if multiplier bit is 1 copy

- 1011 multiplicand (place value)

- 1011 otherwise zero

- 10001111 Product (143 dec)

- Note: need double length result

### Simplifications for Binary Arithmetic

- Partial products are easy to compute:

- If bit is 0, partial product is 0

- If bit is 1, partial product is multiplicand

- Can add each partial product as it is generated, so no storage is needed

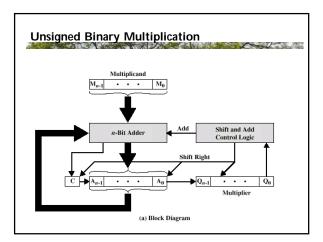

- Binary multiplication of unsigned integers reduces to "shift and add"

# Control logic and registers

- 3 n bit registers, 1 bit carry register CF

- Register set up

- Q register <- multiplier

- M register <- multiplicand

- A register <- 0

- -- CF <- 0

- CF for carries after addition

- Product will be 2n bits in A Q registers

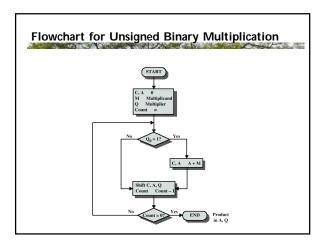

# Multiplication Algorithm Repeat n times: If Q<sub>0</sub> = 1 Add M into A, store carry in CF Shift CF, A, Q right one bit so that: A<sub>n-1</sub> <- CF</li> Q<sub>n-1</sub> <- A<sub>0</sub> Q<sub>0</sub> is lost Note that during execution Q contains bits from both product and multiplier

| Execut | ion of | Examp | ble  |                          |

|--------|--------|-------|------|--------------------------|

| C      | A      | Q     | M    | Initial Values           |

| 0      | 0000   | 1101  | 1011 |                          |

| 0      | 1011   | 1101  | 1011 | Add First                |

| 0      | 0101   | 1110  | 1011 | Shift Cycle              |

| 0      | 0010   | 1111  | 1011 | shift } Second Cycle     |

| 0      | 1101   | 1111  | 1011 | Add } Third Cycle        |

| 0      | 0110   | 1111  | 1011 |                          |

| 1      | 0001   | 1111  | 1011 | Add } Fourth Shift Cycle |

| 0      | 1000   | 1111  | 1011 |                          |

| <ul> <li>When the multiplicand</li> <li>Each addition of the n<br/>must be negative num</li> <li>Sign extend multiplication</li> </ul>          | egative multiplicand<br>ber with 2n bits                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 1001  (9) \\ \times 0011  (3) \\ 00001001  1001 \times 2^{\circ} \\ 0001001  1001 \times 2^{1} \\ 00011011  (27) \end{array}$ | $\begin{array}{ccccc} 1001 & (-7) \\ \times 0011 & (3) \\ \hline 11111001 & (-7) \times 2^{\circ} = (-7) \\ \underline{11110001} & (-7) \times 2^{1} = (-14) \\ \hline 1110001 & (-21) \end{array}$ |

| <ul> <li>(a) Unsigned integers</li> <li>Or sign extend both op<br/>precision</li> <li>Not efficient</li> </ul>                                  | (b) Twos complement integers                                                                                                                                                                        |

### The obvious solution

- · Convert multiplier and multiplicand to unsigned integers

- Multiply

- · If original signs differed, negate result

- · But there are more efficient ways

### Fast multiplication

- Consider the product 6234 \* 99990

- We could do 4 single-digit multiplies and add partial sums

- Or we can express the product as 6234 \* (10<sup>6</sup> - 10<sup>1</sup>)

- In binary x \* 00111100 can be expressed as

- $x * (2^5 + 2^4 + 2^{3+} 2^2) = x * 60$

- We can reduce the number of operations to 2 by observing that 00111100 = 01000000 - 00000010 (64-4 = 60)

- x \* 00111100 = x \* 2<sup>6</sup> x \* 2<sup>2</sup>

- Each block of 1's can be reduced to two operations

- In the worst case 01010101 we still have only 8 operations

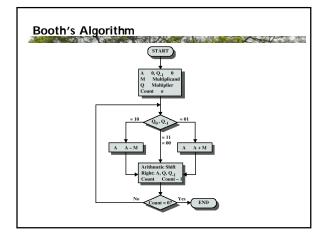

### Booth's Algorithm Registers and Setup

• 3 n bit registers, 1 bit register logically to the right of Q (denoted as  $Q_{-1}$ )

- Register set up

- Q register <- multiplier

- Q<sub>-1</sub> <- 0

- M register <- multiplicand

- A register <- 0

- Count <- n

- Product will be 2n bits in A Q registers

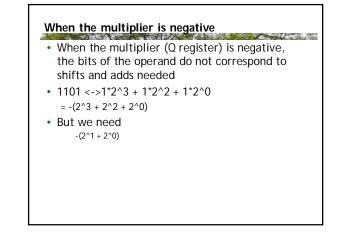

### Booth's Algorithm Control Logic

- Bits of the multiplier are scanned one at a a time (the current bit  $Q_0$ )

- . As bit is examined the bit to the right is considered also (the previous bit  $Q_{-1}$ )

- Then:

- 00: Middle of a string of 0s, so no arithmetic operation. 01: End of a string of is, so add the multiplicand to the left half of the product (A).

10: Beginning of a string of 1s, so subtract the multiplicand from the left half of the product (A).

- 11: Middle of a string of 1s, so no arithmetic operation.

- Then shift A, Q, bit  $Q_{-1}$  right one bit using an •

- arithmetic shift

- In an arithmetic shift, the msb remains unchanged •

| hm (7*3=21)               |

|---------------------------|

|                           |

| nitial Values             |

| A - M First<br>hift Cycle |

| A - M First<br>hift Cycle |

| hift } Second<br>Cycle    |

| A + M Third<br>Cycle      |

| hift ∫ Cycle              |

| hift } Fourth<br>Cycle    |

|                           |

| A    | Q    | Q_1 | м    | C/P | Comment          |

|------|------|-----|------|-----|------------------|

| 0000 | 1101 | 0   | 0010 |     | Initial Values   |

| 1110 | 1101 | 0   | 0010 | 10  | A <- A - 2 = -2  |

| 1111 | 0110 | 1   | 0010 |     | >>1              |

| 0001 | 0110 | 1   | 0010 | 01  | A <- A + 2       |

| 0000 | 1011 | 0   | 0010 |     | >>1              |

| 1110 | 1011 | 0   | 0010 | 01  | A < - A - 2 = -2 |

| 1111 | 0101 | 1   | 0010 |     | >>1              |

| 1111 | 1010 | 1   | 0010 | 11  | >>1 A:Q = -6     |

|      |      |     |      |     |                  |

| A    | Start T | Q_1 |      | -0 (1<br>C/P | 111 = -1)        |

|------|---------|-----|------|--------------|------------------|

| 0000 | -       | -   | 0110 |              | Initial Values   |

| 1010 | 1111    | 1   | 0110 | 10           | A < - A - 6 = -6 |

| 1101 | 0111    | 1   | 0110 |              | >>1              |

| 1110 | 1011    | 1   | 0110 | 11           | >>1              |

| 1111 | 0101    | 1   | 0110 | 11           | >>1              |

| 1111 | 1010    | 1   | 0110 | 11           | >>1 A:Q = -6     |

|      |         |     |      |              |                  |

|      |         |     |      |              |                  |

| Exan | nple: | 3 * | -2 = - | 6 (1 | 110 = -2)          |

|------|-------|-----|--------|------|--------------------|

| A    | Q     | Q_1 | M      | C/P  | Comment            |

| 0000 | 0011  |     |        |      | Initial Values     |

| 0010 | 0011  | 0   | 1110   | 10   | A <- A - (-2) = 2  |

| 0001 | 0001  | 1   | 1110   |      | >> 1               |

| 0000 | 1000  | 1   | 1110   | 11   | >> 1               |

| 1110 | 1000  | 1   | 1110   | 01   | A <- A + (-2) = -2 |

| 1111 | 0100  | 0   | 1110   |      | >>1                |

| 1111 | 1010  | 0   | 1110   | 00   | >> 1 A:Q = -6      |

|      |       |     |        |      |                    |

|      |       |     |        |      |                    |

|      |       |     |        |      |                    |

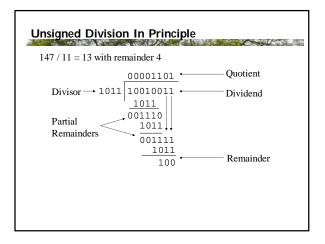

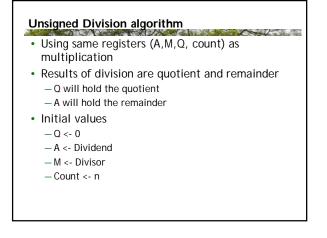

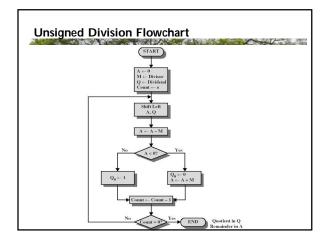

(for computers as well as humans!) - Some processors designed for embedded applications or digital signal processing lack a divide instruction

- · Basically inverse of add and shift: shift and subtract

- Similar to long division taught in grade school

More difficult than unsigned division

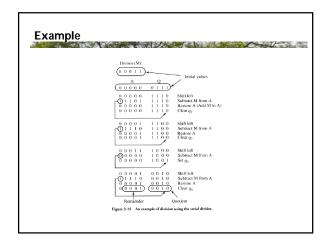

- Algorithm:

- M <- Divisor, A:Q <- dividend sign extended to 2n bits; for example 0111 -> 00000111; 1001-> 11111001 (note that 0111 = 7 and 1001 = -3)

THE SECOND

- 2. Shift A:Q left 1 bit

- 3. If M and A have same signs, perform A <- A-M otherwise perform A <- A + M

- 4. The preceding operation succeeds if the sign of A is unchanged

- If successful, or (A==0 and Q==0) set Q<sub>0</sub> <- 1</li>

If not successful, and (A!=0 or Q!=0) set Q<sub>0</sub> <- 0 and restore the previous value of A</li>

- 5. Repeat steps 2,3,4 for n bit positions in Q

- Remainder is in A. If the signs of the divisor and dividend were the same then the quotient is in Q, otherwise the correct quotient is 0-Q

|      | A A A A A A A A A A A A A A A A A A A |               |      | a second de la companya de |             |

|------|---------------------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| A    | Q                                     | M = 0011      | A    | Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M = 11      |

| 0000 | 0111                                  | Initial value | 0000 | 0111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Initial val |

| 0000 | 1110                                  | shift         | 0000 | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | shift       |

| 1101 |                                       | subtract      | 1101 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | add         |

| 0000 | 1110                                  | restore       | 0000 | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | restore     |

| 0001 | 1100                                  | shift         | 0001 | 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | shift       |

| 1110 |                                       | subtract      | 1110 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | add         |

| 0001 | 1100                                  | restore       | 0001 | 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | restore     |

| 0011 | 1000                                  | shift         | 0011 | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | shift       |

| 0000 |                                       | subtract      | 0000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | add         |

| 0000 | 1001                                  | set $Q_0 = 1$ | 0000 | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | set $Q_0 =$ |

| 0001 | 0010                                  | shift         | 0001 | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | shift       |

| 1110 |                                       | subtract      | 1110 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | add         |

| 0001 | 0010                                  | restore       | 0001 | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | restore     |

|      | (a) (7)/(3)                           |               |      | (b) (7)/(-3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

|      |              |               |      |               | the second    |

|------|--------------|---------------|------|---------------|---------------|

| A    | Q            | M = 0011      | A    | Q             | M = 110       |

| 1111 | 1001         | Initial value | 1111 | 1001          | Initial value |

| 1111 | 0010         | shift         | 1111 | 0010          | shift         |

| 0010 |              | add           | 0010 |               | subtract      |

| 1111 | 0010         | restore       | 1111 | 0010          | restore       |

| 1110 | 0100         | shift         | 1110 | 0100          | shift         |

| 0001 |              | add           | 0001 |               | subtract      |

| 1110 | 0100         | restore       | 1110 | 0100          | restore       |

| 1100 | 1000         | shift         | 1100 | 1000          | shift         |

| 1111 |              | add           | 1111 |               | subtract      |

| 1111 | 1001         | set $Q_0 = 1$ | 1111 | 1001          | set $Q_0 = 1$ |

| 1111 | 0010         | shift         | 1111 | 0010          | shift         |

| 0010 |              | add           | 0010 |               | subtract      |

| 1111 | 0010         | restore       | 1111 | 0010          | restore       |

|      | (c) (-7)/(3) |               |      | (d) (-7)/(-3) |               |

| 2's complement remainders                 |

|-------------------------------------------|

| • 7/3 = 2 R 1                             |

| • 7/-3 = -2 R 1                           |

| • -7 / 3 = -2 R -1                        |

| • -7 / -3 = 2 R -1                        |

| Here the remainder is defined as:         |

| Dividend = Quotient * Divisor + Remainder |

|                                           |

|                                           |

|                                           |

|                                           |

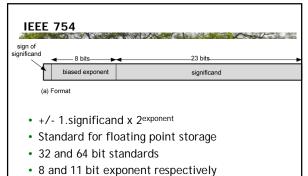

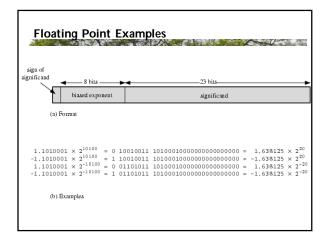

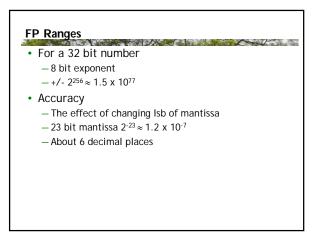

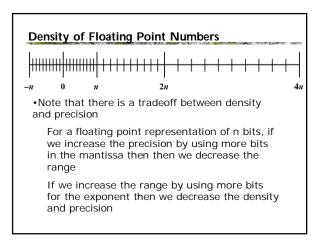

### IEEE-754 Floating Point Numbers

- Format was discussed earlier in class

- Before IEEE-754 each family of computers had proprietary format: Cray, Vax, IBM

- Some Cray and IBM machines still use these formats

- Most are similar to IEEE formats but vary in details (bits in exponent or mantissa):

- IBM Base 16 exponent

- Vax, Cray: bias differs from IEEE

- Cannot make precise translations from one format to another

- Older binary scientific data not easily accessible

• Extended formats (both mantissa and exponent) for intermediate results

### Zero check

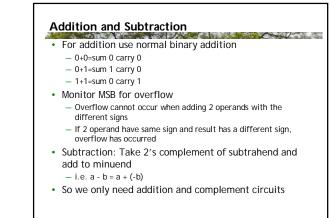

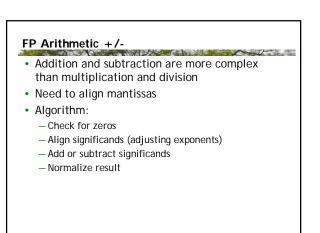

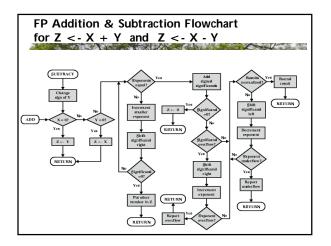

· Addition and subtraction identical except for sign change

The second

• For subtraction, just negate subtrahend (Y in Z = X-Y) then compute Z = X+Y

1

• If either operand is 0 report the other as the result

- Significand Alignment • Manipulate numbers so that both exponents are equal

- Shift number with smaller exponent to the right - if bits are lost they will be less significant

- Repeat Shift mantissa right 1 bit

- Add 1 to exponent

- Until exponents are equal

- If mantissa becomes 0 report other number as result

### Addition

- • Add mantissas together, taking sign into account

- May result in 0 if signs differ

- Can result in mantissa overflow by 1 bit (carry) - Shift mantissa right and increment exponent

- Report error if exponent overflow

### Normalization

- While (MSB of mantissa == 0)

- Shift mantissa left one bit

- Decrement exponent

- Check for exponent underflow

- Round mantissa

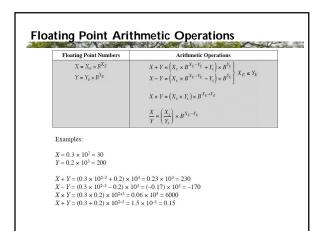

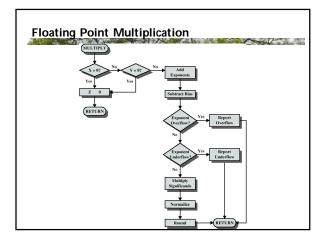

### FP Arithmetic Multiplication and Division

- Simpler processes than addition and subtraction

- Check for zero

- Add/subtract exponents

- Multiply/divide significands (watch sign)

- Normalize

- Round

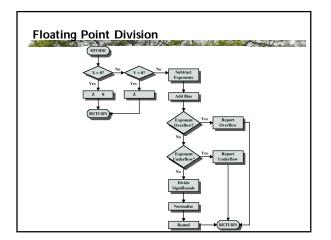

### Division

- If divisor is 0 report error or infinity; dividend 0 then result is 0

- Subtract divisor exponent from dividend exp.

Removes bias so add bias back

- If exponent underflow or overflow, report error — Underflow may be reported as 0 and overflow as infinity

- Divide mantissas as if they were integers (similar to 2's comp mult.)

Note product is twice as long as factors

- Normalize and round

- Same process as addition

- Could result in exponent underflow

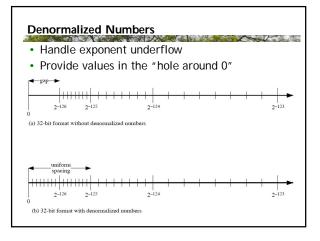

### IEEE Standard for Binary Arithmetic

- Specifies practices and procedures beyond format specification

- Guard bits (intermediate formats)

- Rounding

- Treatment of infinities

- Quiet and signaling NaNs

- Denormalized numbers

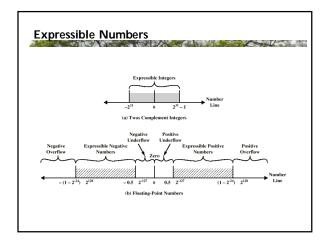

### Precision considerations

Floating point arithmetic is inherently inexact except where only numbers composed of sums of powers of 2 are used

- To preserve maximum precision there are two main techniques:

- Guard bits

- Rounding rules

### Guard bits

- Length of FPU registers > bits in mantissa 1 - Carlos

- Allows some preservation of precision when -aligning exponents for addition

- Multiplying or dividing significands

- We have seen that results of arithmetic can vary when intermediate stores to memory are made in the course of a computation

### Rounding

- · Conventional banker's rounding (round up if 0.5) has a slight bias toward the larger number

- To remove this bias use round-to-even:

- 1.5 -> 2

- 2.5 -> 2

- 3.5 -> 4 4.5 -> 4

- Etc

### IEEE Rounding

TOTAL STREET

- Four types are defined: - Round to nearest (round to even)

- Round to + infinity

- Round to infinity

- Round to 0

### Round to nearest

- • If extra bits beyond mantissa are 100..1.. then round up

- If extra bits are 01... then truncate

- Special case: 10000...0 - Round up if last representable bit is 1

- Truncate if last representable bit is 0

# Round to +/- infinity

- Useful for interval arithmetic

- Result of fp computation is expressed as an interval with upper and lower endpoints

- Width of interval gives measure of precision

- In numerical analysis algorithms are designed to minimize width of interval

### Round to 0

- • Simple truncation, obvious bias

- May be needed when explicitly rounding following operations with transcendental functions

### Infinities

- Infinity treated as limiting case for real arithmetic

- Most arithmetic operations involving infinities produce infinity

### **Quiet and Signaling NaNs**

- NaN = Not a Number

- Signaling NaN causes invalid operation exception if used as operand

- Quiet NaN can propagate through arithmetic operations without raising an exception

- Signaling NaNs are useful for initial values of uninitialized variables

- Actual representation is implementation (processor) specific

| Operation       | Quiet NaN Produced by                                |

|-----------------|------------------------------------------------------|

| Any             | Any operation on a signaling Nal                     |

|                 | Magnitude subtraction of infinitie                   |

|                 | $(+\infty) + (-\infty)$                              |

| Add or subtract | $(-\infty) + (+\infty)$                              |

|                 | $(+\infty) - (+\infty)$                              |

|                 | $(-\infty) - (-\infty)$                              |

| Multiply        | 0 × ∞                                                |

| Division        | $\frac{0}{0}$ or $\frac{\infty}{\infty}$             |

| Remainder       | $x \text{ REM } 0 \text{ or } \infty \text{ REM } y$ |

| Square root     | $\sqrt{x}$ where $x < 0$                             |

### **Unnormalized Numbers**

- Denormalized numbers have fewer bits of precision than normal numbers

- When an operation is performed with a denormalized number and a normal number, the result is called an "unnormal" number

- Precision is unknown

- FPU can be programmed to raise an exception for unnormal computations